共模电感漏感对变压器差模干扰抑制的贡献与控制方法

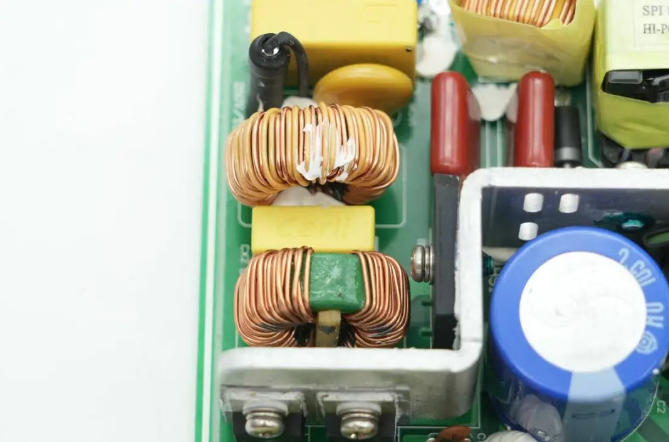

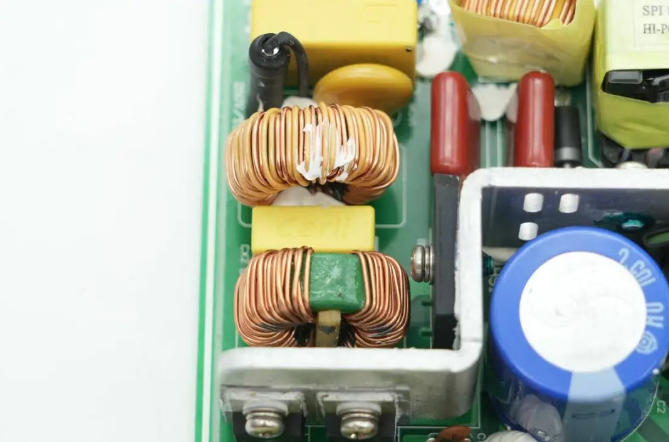

在开关电源的输入端,共模电感的主要任务是抑制共模噪声——这几乎是所有工程师的共识。然而,共模电感身上还有一个常被忽视的“隐性功能”:漏感。由于两组绕组在磁芯上无法实现100%的磁耦合,总会有一部分磁通从绕组逸散而不穿过对侧线圈,这部分“走失”的磁通就形成了漏感。这颗漏感虽然微小,通常仅为共模电感量的0.5%至2%,却恰好串联在L线与N线之间,天然地构成了一个差模滤波元件。若能合理利用并精确控制这一漏感,往往可以在不增加额外差模电感的前提下,显著改善变压器输入端的差模干扰抑制能力。

差模干扰是指沿着L-N回路流动的噪声电流,其能量主要集中在较低频段(150kHz至5MHz)。在常规EMI滤波器中,抑制差模噪声主要依靠X电容和独立的差模电感。但共模电感的漏感与X电容恰好形成一个LC低通滤波器,这意味着,只要漏感足够大,就能在不增加任何元件的条件下获得额外的差模衰减。以一颗20mH的共模电感为例,其漏感通常在100μH至400μH之间。搭配0.47μF的X电容,形成的差模滤波截止频率约为23kHz至36kHz,远低于150kHz的传导测试起始频率,意味着在150kHz以上频段,该LC网络已经进入衰减区,能够提供20dB/dec的差模抑制斜率。实测数据显示,在相同X电容配置下,漏感为300μH的共模电感比漏感仅50μH的产品,在150kHz至1MHz频段内的差模插入损耗高出约8dB至12dB。这相当于多串联了一颗小型差模电感,却无需额外的PCB面积和成本。然而,漏感并非越大越好。过大的漏感会降低共模电感的共模抑制能力——因为漏感本质上是耦合损失的体现,漏感越大意味着磁耦合越差,共模电感量可能低于标称值。同时,漏感与分布电容之间可能形成并联谐振,在特定频率点产生阻抗低谷,反而削弱滤波效果。因此,控制漏感在合理范围内,使其既能贡献差模抑制,又不损害共模性能,才是工程设计的关键。

控制漏感的工程方法平尚科技在共模电感的设计与制造中,总结出以下几种调控漏感的有效手段:绕组不对称法:有意使两组绕组在磁芯上的绕制位置不完全对称,例如让一个绕组紧贴磁芯内侧、另一个绕组靠外侧,或者采用不同匝数的非平衡绕制。这种方法可使漏感在较大范围内变化(从电感量的0.2%到5%)。但需注意,绕组不对称会轻微降低共模电感量,适用于共模抑制裕量充足的应用。磁芯结构选择:环形磁芯的漏感通常较小(约0.5%),因为磁路封闭,磁通泄漏少。而U型或E型磁芯因存在开放磁路间隙,漏感可达1%至2%。因此,若希望获得较大的漏感以增强差模滤波,可优先选用U型或E型磁芯共模电感。分槽骨架法:在绕线骨架上设置隔槽,将两组绕组分别置于不同槽内,强制增加漏磁路径。这种方法可使漏感达到电感量的3%至5%,但共模电感量会相应下降,且体积增大。适用于对差模抑制要求极高、且空间充足的工业电源。绕组结构调控:采用多层分段绕制或特定层间绝缘厚度,可微调漏感。平尚科技通过控制绕线张力、层间绝缘层厚度(0.05mm至0.2mm),将漏感的生产公差控制在±15%以内,满足批量化一致性要求。工程案例:利用漏感省去一颗差模电感某120W LED驱动电源在传导测试中,150kHz至500kHz频段的差模噪声超标约5dB。原EMI滤波器已配置0.68μF X电容和一颗10mH共模电感(漏感约80μH)。平尚科技在不改变PCB布局的前提下,将共模电感更换为同封装但漏感优化至250μH的定制型号(U型磁芯,绕组略微不对称绕制)。更换后,相同X电容下150kHz频点的差模噪声降低9dB,顺利通过EN55015认证,且共模抑制能力未下降(因为共模电感量仍保持在9.8mH)。该方案为客户节省了一颗差模电感的物料成本和贴片费用,每万套节约近万元。对比分析:漏感滤波 vs 独立差模电感

从对比可以看出,利用漏感是一种“低成本、小体积”的优化手段,但无法完全替代大感值的独立差模电感。工程上通常先尝试优化漏感,若仍不足再追加独立电感。共模电感的漏感不是设计缺陷,而是一把可以主动掌控的“双刃剑”。善用其差模滤波贡献,能在不增加成本与面积的前提下提升EMI性能;忽视其控制,则可能导致共模抑制下降或谐振问题。平尚科技基于对磁芯材料、绕组结构与漏感关系的深入理解,为国内变压器厂商提供从漏感定制到EMC整改的全流程支持——让每一颗共模电感既当好共模噪声的“克星”,也做好差模干扰的“帮手”。