解密400G AI交换机核心ASIC供电:多相VRM中贴片电容的PDN阻抗优化

在400G及更高速率的AI数据中心交换机中,核心交换ASIC芯片的功耗已突破数百瓦,其供电设计堪称电源领域的“极限挑战”。为了在纳秒级时间内响应ASIC突发的大电流负载,并维持极低的电压纹波,多相电压调节模块(多相VRM)成为标准方案。而决定这一供电网络性能成败的关键,并非仅在于功率级,更在于其电源分配网络(PDN)的阻抗特性。在这一精密体系中,贴片电容,特别是多层陶瓷电容(MLCC),从被动的滤波元件转变为主动塑造PDN频率响应的核心角色。平尚科技凭借在工业级高密度电源领域的深入实践,正帮助客户驾驭PDN阻抗优化这一复杂课题。

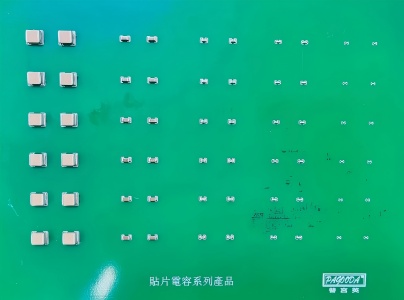

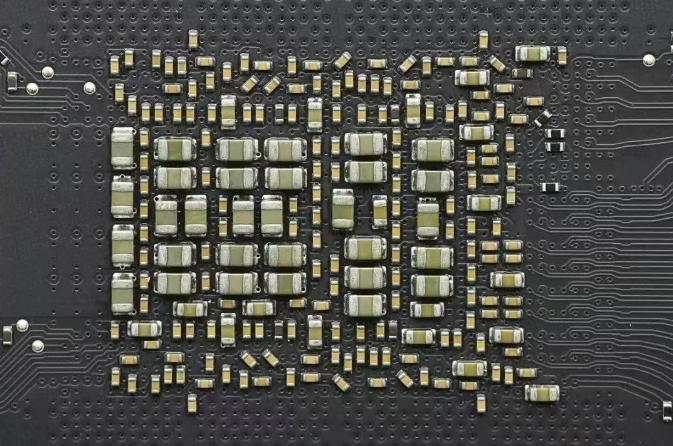

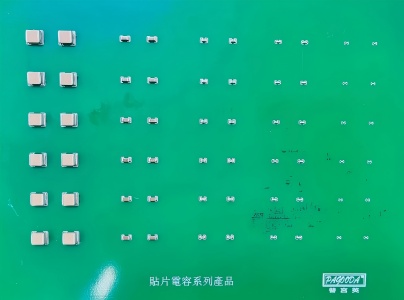

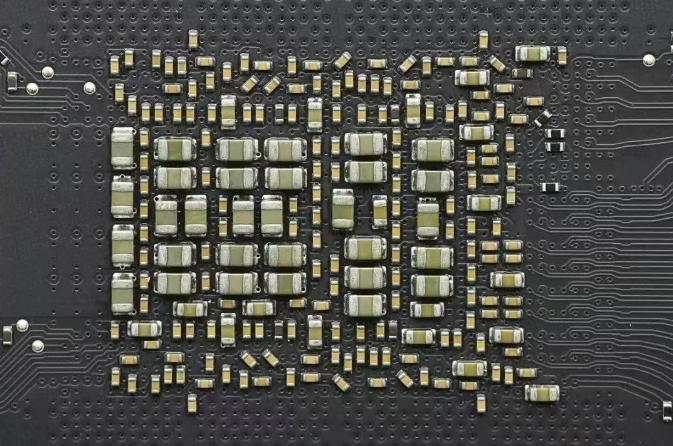

PDN阻抗优化,简言之,是确保从VRM输出端到ASIC电源引脚之间的阻抗,在从直流到数百MHz的宽频带内,始终低于目标阻抗(Target Impedance)。目标阻抗由允许的最大电压波动除以负载瞬态电流变化率决定,对于先进ASIC,这一值可能低至1毫欧甚至以下。一个理想化的PDN阻抗曲线,应呈现平坦的低阻抗“凹槽”,而贴片电容正是填平这个凹槽的主要“材料”。在这一优化过程中,不同封装尺寸和介质材料的贴片电容,因其固有的寄生参数不同,负责覆盖不同的频段:大容量、中低压电容负责中低频段:通常采用1210或0805封装的X7R/X6S介质MLCC,容值在10μF至100μF范围,用于提供 bulk 电容,处理kHz至数百kHz频段的电流需求。其等效串联电阻(ESR)和等效串联电感(ESL)共同决定了其中频阻抗峰。国内先进工艺已能使0805封装下的22μF/6.3V电容的ESR稳定在2毫欧左右,ESL在0.5纳亨级别,为构建低阻抗基底提供可能。小尺寸、低ESL电容主宰高频段:当频率进入数MHz至百MHz范围,大容量电容因ESL而失效。此时,必须依靠大量0402、0201乃至01005封装的MLCC阵列。这些“小兵”凭借极低的ESL(可低于0.2纳亨)和极近的摆放位置(紧靠ASIC背面),为GHz级别的瞬态电流提供“最近距离”的响应。其容值通常在0.1μF至1μF之间,选用C0G或低损耗X7R介质以确保参数稳定。国内供应链已能稳定提供ESL值经过优化控制的0201封装高频MLCC。封装参数在此处直接转化为电气性能:更小的封装(如0201对比0603)通常意味着更低的寄生电感,但也会牺牲单颗电容的容值和耐压。因此,PDN优化是一个典型的“用数量换性能”的过程——通过部署数十至数百颗小尺寸电容组成的密集阵列,来并联出极低的整体ESL和足够的有效容值。电容在PCB上的布局、过孔连接方式,甚至其与电源/地平面的相对位置,都成为影响最终PDN阻抗的“封装外延参数”。

平尚科技在服务交换机客户时,不仅提供符合工业级可靠性要求的全系列贴片电容,更参与到前期的PDN协同设计中。通过提供基于实际电容型号的精确SPICE模型(包含ESR、ESL等参数),帮助客户在仿真阶段就精准预测阻抗曲线,从而优化电容的种类、数量、容值配比与布局方案。例如,通过仿真可能发现,在特定频点存在阻抗尖峰,此时可能需要调整不同封装电容的比例,或引入特定容值的去耦电容来“填谷”。因此,为400G AI交换机ASIC供电进行PDN阻抗优化,本质上是一场在三维空间(PCB布局)和频率维度上进行的、以贴片电容为关键武器的精密“排兵布阵”。其目标是在有限的空间内,构建一条从VRM到晶体管、跨越多个数量级频率的“超低阻抗高速公路”。平尚科技通过提供高性能、高一致性的电容产品与深度的应用技术支持,助力客户攻克这一高速网络设备的核心供电挑战,确保每一颗ASIC都能获得纯净、迅捷的能源,驱动数据洪流在超高速网络中无阻奔涌。