#### 平尚科技

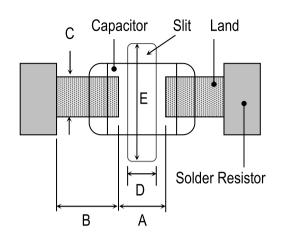

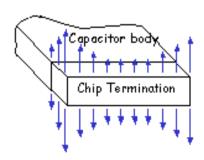

2.1 Size and recommend land dimensions for reflow soldering.

| EIA Code | Chip (mm) |      | Land (mm) |         |         |         |         |

|----------|-----------|------|-----------|---------|---------|---------|---------|

|          | L         | W    | Α         | В       | С       | D       | Е       |

| 0201     | 0.60      | 0.30 | 0.2~0.3   | 0.2~0.4 | 0.2~0.4 |         |         |

| 0402     | 1.00      | 0.50 | 0.3~0.5   | 0.3~0.5 | 0.4~0.6 |         | 1       |

| 0603     | 1.60      | 0.80 | 0.4~0.6   | 0.6~0.7 | 0.6~0.8 |         |         |

| 0805     | 2.00      | 1.25 | 0.7~0.9   | 0.6~0.8 | 0.8~1.1 |         | 1       |

| 1206     | 3.20      | 1.60 | 2.2~2.4   | 0.8~0.9 | 1.0~1.4 | 1.0~2.0 | 3.2~3.7 |

| 1210     | 3.20      | 2.50 | 2.2~2.4   | 1.0~1.2 | 1.8~2.3 | 1.0~2.0 | 4.1~4.6 |

| 1808     | 4.60      | 2.00 | 2.8~3.4   | 1.8~2.0 | 1.5~1.8 | 1.0~2.8 | 3.6~4.1 |

| 1812     | 4.60      | 3.20 | 2.8~3.4   | 1.8~2.0 | 2.3~3.0 | 1.0~2.8 | 4.8~5.3 |

| 1825     | 4.60      | 6.35 | 2.8~3.4   | 1.8~2.0 | 5.1~5.8 | 1.0~4.0 | 7.1~8.3 |

| 2208     | 5.70      | 2.00 | 4.0~4.6   | 2.0~2.2 | 1.5~1.8 | 1.0~4.0 | 3.6~4.1 |

| 2211     | 5.70      | 2.80 | 4.0~4.6   | 2.0~2.2 | 2.0~2.6 | 1.0~4.0 | 4.4~4.9 |

| 2220     | 5.70      | 5.00 | 4.0~4.6   | 2.0~2.2 | 3.5~4.8 | 1.0~4.0 | 6.6~7.1 |

| 2225     | 5.70      | 6.35 | 4.0~4.6   | 2.0~2.2 | 5.1~5.8 | 1.0~4.0 | 7.1~8.3 |

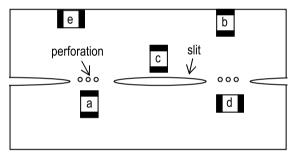

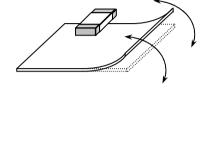

2.2 Mechanical strength varies according to location of chip capacitors on the P.C. board.

Design layout of components on the PC board such a way to minimize the stress imposed on the components, upon flexure of the boards in depanelization or other processes.

Component layout close to the edge of the board or the "depanelization line" is not recommended. Susceptibility to stress is in the order of: a>b>c and d>e

# 2.3 Layout Recommendation

| Example        | Use of Common                                          | Solder With Chassis       | Use of Common Solder |

|----------------|--------------------------------------------------------|---------------------------|----------------------|

|                | Solder Land                                            |                           | Land With Other SMD  |

| Need to Avoid  | Chip Solder  Adhesive PCB Solder Land                  | Chassis  Excessive Solder | Solder Land          |

| Recommendation | Lead Wire Chip Solder Resist  Adhesive PCB Solder Land | Solder Resist             |                      |

## 3. Mounting

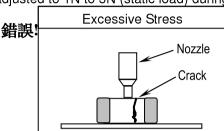

3.1 Sometimes crack is caused by the impact load due to suction nozzle in pick and place operation.

In pick and place operation, if the low dead point is too low, excessive stress is applied to component. This may cause cracks in the ceramic capacitor, therefore it is required to move low dead point of a suction nozzle to the higher level to minimize the board warp age and stress on the components. Nozzle pressure is typically

adjusted to 1N to 3N (static load) during the pick and place operation.

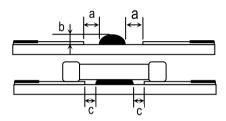

#### 3.2 Amount of Adhesive

| Example: 0805 & 1206 |                              |  |  |  |  |

|----------------------|------------------------------|--|--|--|--|

| а                    | 0.2mm min.                   |  |  |  |  |

| b                    | 70 ~ 100 μm                  |  |  |  |  |

| С                    | Do not touch the solder land |  |  |  |  |

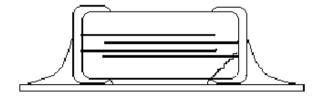

### 4. Soldering

### 4.1. Wave Soldering

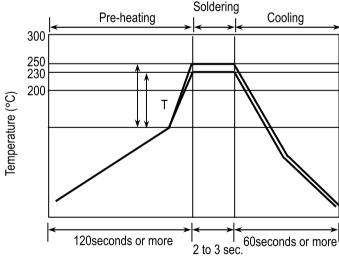

Most of components are wave soldered with solder at 230 to 250 ℃. Adequate care must be taken to prevent the potential of thermal cracks on the ceramic capacitors. Refer to the soldering methods below for optimum soldering benefits.

# **Recommend flow soldering temperature Profile**

| Soldering Method | Change in Temp.( ) |

|------------------|--------------------|

| 1206 and Under   | T ≤ 100~130 max.   |

To optimize the result of soldering, proper preheating is essential:

- 1) Preheat temperature is too low

- a. Flux flows to easily

- b. Possibility of thermal cracks

- 2) Preheat temperature is too high

- a. Flux deteriorates even when oxide film is removed

- b. Causes warping of circuit board

- c. Loss of reliability in chip and other components

## Cooling Condition:

Natural cooling using air is recommended. If the chips are dipped into a solvent for cleaning, the temperature difference ( T) between the solvent and the chips must be less than 100 ℃.

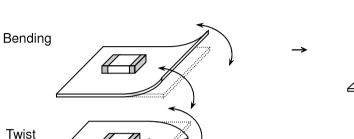

## 5. Handling after chip mounted

5.1 Proper handling is recommended, since excessive bending and twist of the board, depends on the orientation of the chip on the board, may induce mechanical stress and cause internal crack in the capacitor.

Higher potential of crack

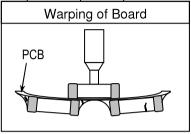

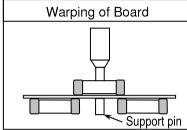

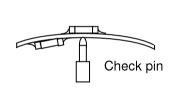

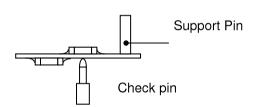

5.2 There is a potential of crack if board is warped due to excessive load by check pin

- 5.3 Mechanical stress due to warping and torsion.

- (a) Crack occurrence ratio will be increased by manual separation.

- (b) Crack occurrence ratio will be increased by tensile force, rather than compressive force.

:Tensile Stress

:Compressive Stress

Capacitor Stress Analysis

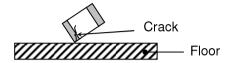

# 6. Handling of Loose Chip Capacitor

6.1 If dropped the chip capacitor may crack.

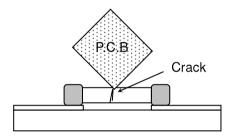

6.2 In piling and stacking of the P.C. boards after mounting for storage or handling, the corner of the P.C. board may hit the chip capacitor mounted on another board to cause crack.

# 7. Safekeeping condition and period

For safekeeping of the products, we recommend to keep the storage temperature between +5 to +40 °C and under humidity of 20 to 75% RH. The shelf life of capacitors is 6 months.